# TELECOMMS INTEGRATED CIRCUIT HANDBOOK

© The Plessey Company Limited July 1981 Publication No. P.S. 1913

This publication is issued to provide outline information only and (unless specifically agreed to the contrary by the Company in writing) is not to form part of any order or contract or be regarded as a representation relating to the products or services concerned. We reserve the right to alter without notice the specification, design, price or conditions of supply of any product or service.

# **Contents**

|                      | Page |

|----------------------|------|

| Product index        | 5    |

| Selection guide      | 7    |

| Quality data         | 9    |

| Semi-custom design   | 12   |

| Technical data       | 15   |

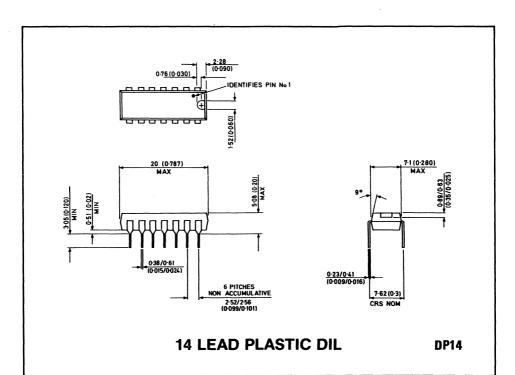

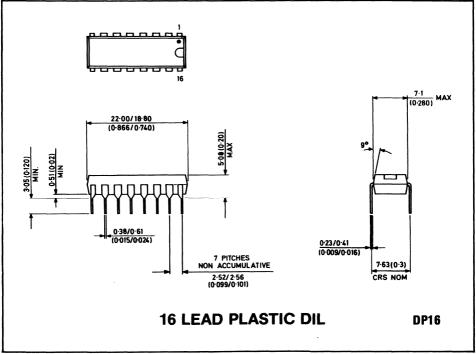

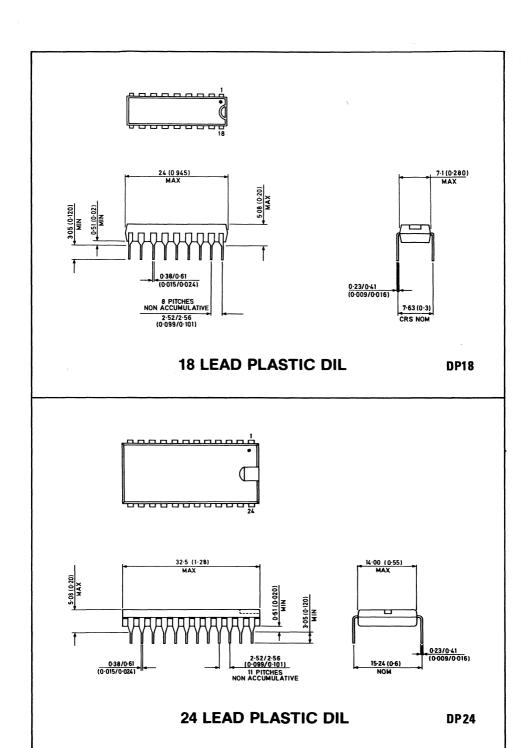

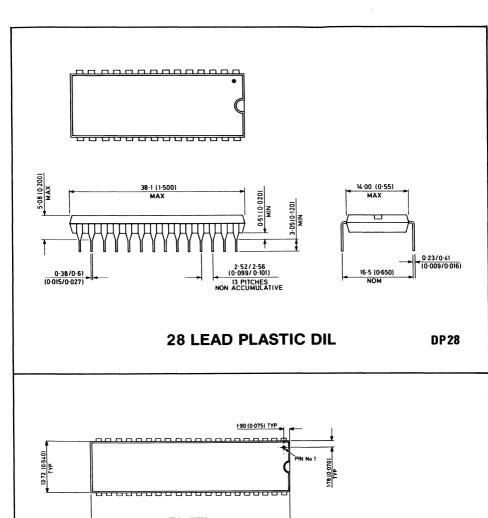

| Package outlines     | 181  |

| Ordering information | 193  |

| Plessey World Wide   | 195  |

# Product index

### N-Channel MOS

| TYPE No.                                                                                                                                                                | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | PAGE                                                                          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|

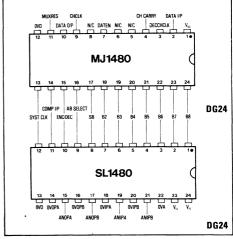

| MJ1410<br>MJ1444<br>MJ1445<br>MJ1446<br>MJ1471<br>MJ1480<br>MJ2812<br>MJ2813<br>MJ2841                                                                                  | 8-bit format converter HDB3 encoder/decoder Time slot zero transmitter Time slot zero receiver Time slot access AMI/HDB3 encoder/decoder Digital controller for use with SL1480 in PCM A-law Codec 32 x 8-bit FIFO memory 32 x 9-bit FIFO memory 64 x 4-bit FIFO memory                                                                                                                                                                                                                                                                                                                                                                         | 17<br>23<br>29<br>33<br>37<br>41<br>47<br>61<br>61<br>67                      |

| CMOS                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                               |

| MV21SC14<br>MV23SC16<br>MV41SC04<br>MV4311<br>MV4320<br>MV4322<br>MV4325<br>MV4325<br>MV4326<br>MV4330<br>MV4331<br>MV4332<br>MV4368<br>MV4511<br>MV68SC02<br>MV74SC137 | 1024 x 4-bit static RAM 2048 x 8-bit ROM Quad low voltage to high voltage level translator Latched Hex to 7-segment LED driver Keypad pulse dialler with M1 masking Keypad pulse dialler with M2 masking Keypad pulse dialler with selectable interdigit pause Programmable keypad pulse dialler with M1 masking Programmable keypad pulse dialler with M2 masking 30-bit static shift register with synchronous reset 30-bit static shift register 32-bit static shift register Latched Hex to 7-segment LED driver Latched BCD to 7-segment LED driver 8-bit microprocessor 1 of 8 octal decoders/demultiplexers, latched I/Ps, inverted O/Ps | 71<br>75<br>79<br>83<br>91<br>91<br>95<br>95<br>101<br>101<br>83<br>83<br>105 |

| MV74SC138                                                                                                                                                               | 1 of 8 octal decoders/demultiplexers, non-latching I/Ps, inverted outputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 111                                                                           |

| MV74SC139<br>MV74SC237                                                                                                                                                  | Dual 1 of 4 octal decoders/demultiplexers, inverted O/Ps 1 of 8 octal decoders/demultiplexers, latched I/Ps, non-inverted outputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 111<br>111                                                                    |

| MV74SC238                                                                                                                                                               | 1 of 8 octal decoders/demultiplexers, non-latching I/Ps, non-inverted O/Ps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 111                                                                           |

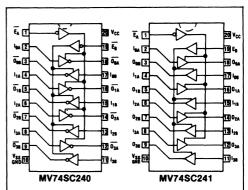

| MV74SC239<br>MV74SC240                                                                                                                                                  | Dual 1 of 4 octal decoders/demultiplexers, non-inverted O/Ps Three-state octal inverting, bi-directional, buffers/linedrivers Three-state octal non-inverting, bi-directional, buffers/line-                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 111<br>117<br>117                                                             |

| MV74SC241                                                                                                                                                               | drivers with complementary enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | , , ,                                                                         |

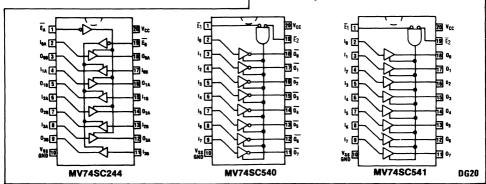

| MV74SC244          | Three-state octal non-inverting, bi-directional buffers/line-drivers                             | 117       |

|--------------------|--------------------------------------------------------------------------------------------------|-----------|

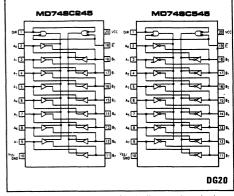

| MV74SC245          | Octal bus transceivers with 3-state buffered O/Ps,                                               | 121       |

|                    | non-inverting                                                                                    | -         |

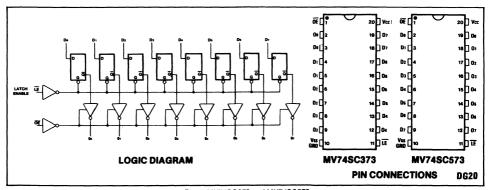

| MV74SC373          | Three-state octal D-type transparent latches, non-inverted O/Ps                                  | 125       |

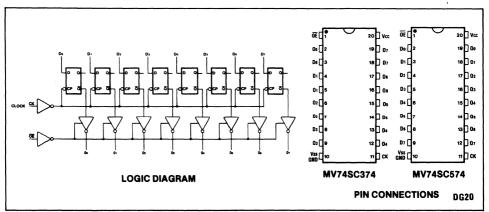

| MV74SC374          | Three-state octal D-type edge-triggered flip-flops, non-inverted O/Ps                            | 125       |

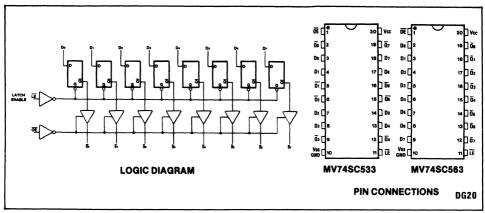

| MV74SC533          | Three-state octal D-type transparent latches, inverted O/Ps                                      | 125       |

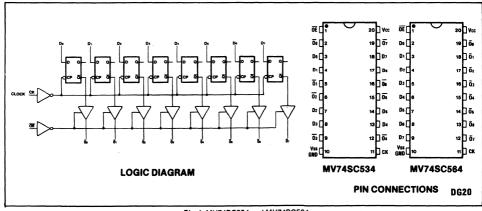

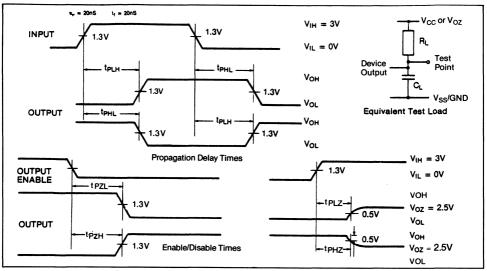

| MV74SC534          | Three-state octal D-type edge-triggered flip-flops, inverted O/Ps                                | 125       |

| MV74SC540          | Three-state octal inverting, uni-directional buffers/linedrivers                                 | 117       |

| MV74SC541          | Three-state octal non-inverting, uni-directional buffers/linedrivers                             | 117       |

| MV74SC545          | Octal bus transceivers with 3-state buffered O/Ps, inverting                                     | 121       |

| MV74SC563          | Three-state octal transparent latches, inverted O/Ps                                             | 125       |

| MV74SC564          | Three-state octal D-type edge-triggered flip-flops, inverted O/Ps                                | 125       |

| MV74SC573          | Three-state octal transparent latches, non-inverted O/Ps                                         | 125       |

| MV74SC574          | Three-state octal D-type edge-triggered flip-flops, non-inveted O/Ps                             | 125       |

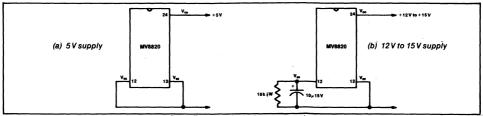

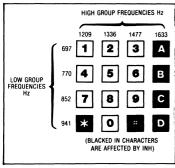

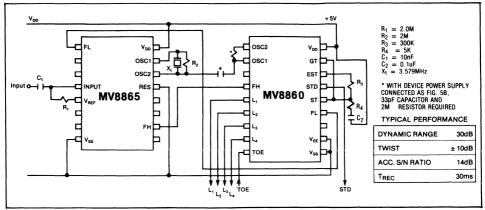

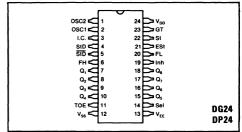

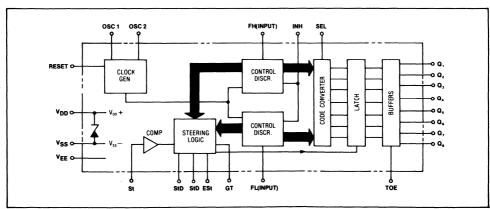

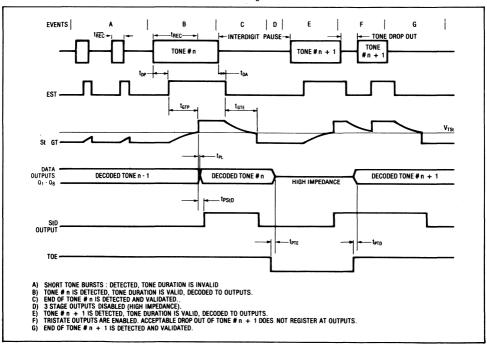

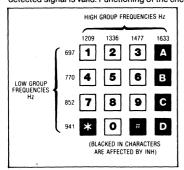

| MV8820             | DTMF decoder with selectable 2 of 8-bit binary or Hex plus GI AY-5-9100 output codes             | 129       |

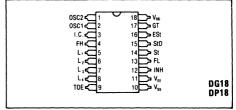

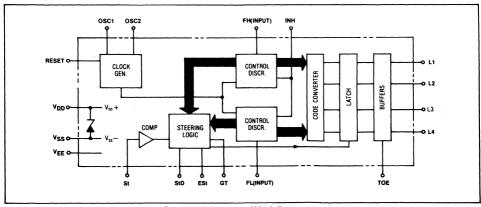

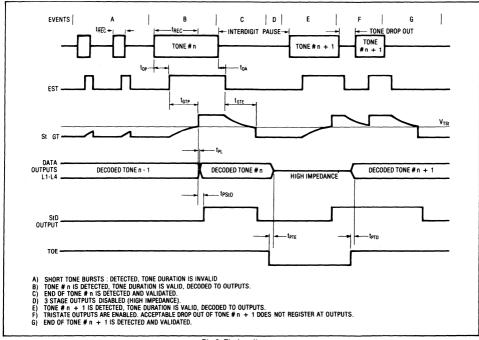

| MV8860             | DTMF decoder with 4-bit binary output                                                            | 133       |

| MV8862             | DTMF decoder with selectable 2 of 8-bit binary or                                                | 141       |

| MV8863             | Hex output codes DTMF decoder, alternative output format version of                              | 141       |

| B41/0005           | MV8862                                                                                           |           |

| MV8865             | DTMF filter                                                                                      | 149       |

| Bipolar            |                                                                                                  |           |

| SL792              | Capacitance microphone amplifier (PVDF)                                                          | 155       |

| SL793<br>SL1001A   | Capacitance microphone amplifier (Electret)                                                      | 159       |

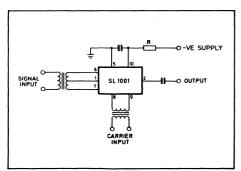

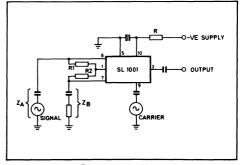

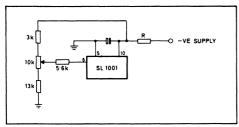

| SL1001A<br>SL1021A | Modulator/demodulator                                                                            | 163       |

| SL1021A<br>SL1021B | Channel amplifier, +10dBm output level                                                           | 167       |

| SL1480             | Channel amplifier, +13dBm output level Analogue processor for use with MJ1480 in PCM A-law Codec | 167       |

| SL1496C            | Double-balanced modulator/demodulator (0°C to +70°C)                                             | 47<br>171 |

| SL1596C            | Double-balanced modulator/demodulator (-55°C to +125°C)                                          | 171       |

| SP1404BW           | High voltage interface circuit                                                                   | 175       |

| SP1450B            | 34 Mbit/s PCM signal monitor                                                                     | 177       |

| SP1450B(B)         | As SP1450B but screened to MIL-STD-883, Method 5004,                                             | .,,       |

|                    | Class B                                                                                          | 177       |

| SP1455B            | 140 Mbit/s PCM signal monitor                                                                    | 177       |

| SP1455B(B)         | As SP1455B but screened to MIL-STD-883, Method 5004.                                             |           |

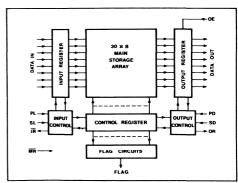

|                    | Class B                                                                                          | 177       |

# Selection guide

|                                                                      |                                                                                                                                                                                                                        | <b>EQUIVALENT</b>          | PAGE                            |

|----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|---------------------------------|

|                                                                      | MOS DATA COMMUNICATIONS                                                                                                                                                                                                |                            |                                 |

| CIRCUITS<br>MJ2812<br>MJ2813<br>MJ2841                               | 32 x 8-bit FIFO memory<br>32 x 9-bit FIFO memory<br>64 x 4-bit FIFO memory                                                                                                                                             | AM2812<br>AM2813<br>AM2841 | 61<br>61<br>67                  |

| MJ1410<br>MJ1440<br>MJ1444                                           | MOS PCM CIRCUITS 8-bit format converter HDB3 encoder/decoder Time slot zero transmitter                                                                                                                                |                            | 17<br>23<br>29<br>33            |

|                                                                      | Time slot zero receiver Time slot access AM1/HDB3 encoder/decoder 8-bit PCM A-law Codec                                                                                                                                | CD22103                    | 37<br>41<br>47                  |

| MODULATOI<br>SL1001A<br>SL1496C                                      | RS  1MHz modulator  20MHz double-balanced modulator/ demodulator (commercial)                                                                                                                                          | MC1496G/L/P                | 163<br>171                      |

| SL1596C                                                              | 20MHz double-balanced modulator/<br>demodulator (MIL)                                                                                                                                                                  | MC1596G/L                  | 171                             |

| TELEPHONE<br>SL792                                                   | COMMUNICATIONS CIRCUITS Capacitance microphone amplifier (PVDF)                                                                                                                                                        |                            | 155                             |

| SL793                                                                | Capacitance microphone amplifier (Electret)                                                                                                                                                                            |                            | 159                             |

| SL1021A<br>SL1021B<br>SP1450B<br>SP1450B(B)<br>SP1455B<br>SP1455B(B) | +10dBm channel amplifier<br>+13dBm channel amplifier<br>34 Mbit/s PCM signal monitor<br>As SP1450B but screened to<br>MIL-STD-883, Method 5004, Class B<br>140 Mbit/s PCM signal monitor<br>As SP1455B but screened to |                            | 167<br>167<br>177<br>177<br>177 |

| INTERFACE<br>SP1404BW                                                | MIL-STD-883, Method 5004, Class B  CIRCUITS  High voltage interface                                                                                                                                                    | ITT7163                    | 175                             |

| CMOS TELE                                                            | PHONE DIALLING CIRCUITS —                                                                                                                                                                                              |                            |                                 |

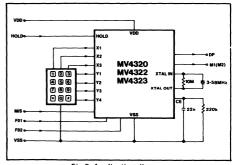

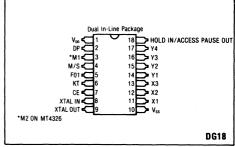

| LOOP DISC<br>MV4320<br>MV4322<br>MV4323                              | Keypad pulse dialler with M1 masking<br>Keypad pulse dialler with M2 masking<br>Keypad pulse dialler with selectable<br>interdigit pause                                                                               | DF320                      | 91<br>91<br>91                  |

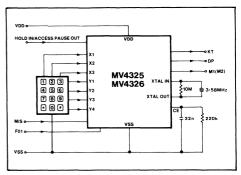

| MV4325                                                               | Programmable keypad pulse dialler with M1 masking                                                                                                                                                                      |                            | 95                              |

| MV4326                                                               | Programmable keypad pulse dialler with M2 masking                                                                                                                                                                      |                            | 95                              |

| CMOS TELE DTMF or MF                                                                                             | PHONE DIALLING CIRCUITS —                                                             |                               |                 |  |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|-------------------------------|-----------------|--|--|--|--|--|

| MV8820                                                                                                           | DTMF decoder with selectable 2 of 8-bit binary or Hex plus GI AY-5-9100 output -codes |                               | 129             |  |  |  |  |  |

| MV8860 DTMF decoder with 4-bit binary output DTMF decoder with selectable 2 of 8-bit binary or Hex. output codes |                                                                                       |                               |                 |  |  |  |  |  |

| MV8863 DTMF decoder, alternative output format version of MV8862                                                 |                                                                                       |                               |                 |  |  |  |  |  |

| MV8865                                                                                                           | DTMF filter                                                                           |                               | 149             |  |  |  |  |  |

| CMOS EDP                                                                                                         | PRODUCTS                                                                              |                               |                 |  |  |  |  |  |

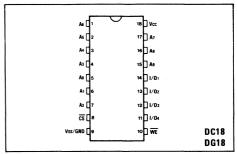

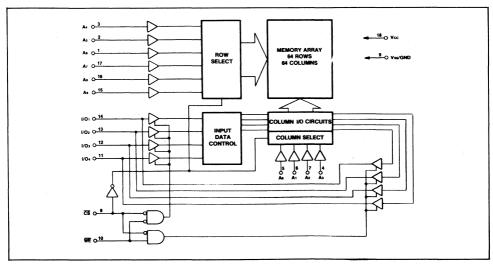

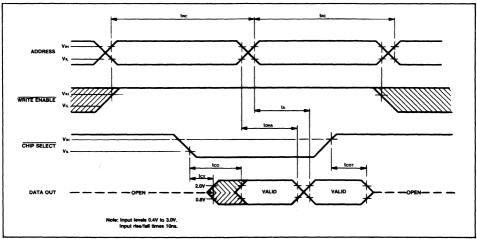

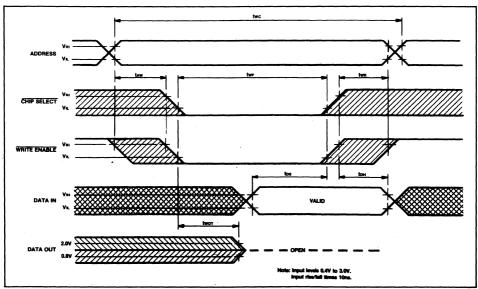

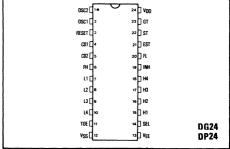

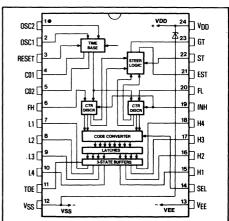

| MV21SC14<br>MV23SC16<br>MV68SC02                                                                                 | 1024 x 4-bit static RAM<br>2048 x 8-bit ROM<br>8-bit Microprocessor                   | 2114,µPD444<br>2316<br>MC6802 | 71<br>75<br>105 |  |  |  |  |  |

| CMOS OCT                                                                                                         |                                                                                       |                               | , 50            |  |  |  |  |  |

| Decoders/De                                                                                                      |                                                                                       |                               |                 |  |  |  |  |  |

| MV74SC137                                                                                                        |                                                                                       | 74LS137                       | 111             |  |  |  |  |  |

| MV74SC138<br>MV74SC139                                                                                           |                                                                                       | 74LS138                       | 111             |  |  |  |  |  |

| MV74SC237/23                                                                                                     | 8:239                                                                                 | 74LS139                       | 111<br>111      |  |  |  |  |  |

| Buffers/Line                                                                                                     |                                                                                       |                               | 111             |  |  |  |  |  |

| MV74SC240/24                                                                                                     |                                                                                       | 741 5040/044                  | 447             |  |  |  |  |  |

|                                                                                                                  | 1,2 1 1,0 10/01                                                                       | 74LS240/244;<br>241;540/541   | 117             |  |  |  |  |  |

| Transceivers                                                                                                     |                                                                                       | 211,010,011                   |                 |  |  |  |  |  |

| MV74SC245                                                                                                        |                                                                                       | 74LS245/645                   | 121             |  |  |  |  |  |

| MV74SC545                                                                                                        |                                                                                       | 74LS640                       | 121             |  |  |  |  |  |

| Transparent I                                                                                                    | Latches                                                                               |                               | ,_,             |  |  |  |  |  |

| MV74SC373                                                                                                        |                                                                                       | 74LS363/373                   | 125             |  |  |  |  |  |

| MV74SC573,53                                                                                                     | 3/563                                                                                 |                               | 125             |  |  |  |  |  |

| Edge-Trigger                                                                                                     | ed D-Type Flip-Flops                                                                  |                               |                 |  |  |  |  |  |

| MV74SC374                                                                                                        | 21                                                                                    | 74LS374,                      | 125             |  |  |  |  |  |

| MV7460574.50                                                                                                     | 4/504                                                                                 | 74LS364                       |                 |  |  |  |  |  |

| MV74SC574,534                                                                                                    | 4/564                                                                                 |                               | 125             |  |  |  |  |  |

| CMOS INTER                                                                                                       | RFACE AND DISPLAY DRIVER                                                              |                               |                 |  |  |  |  |  |

| MV41SC04                                                                                                         | Quad low voltage to high voltage translator                                           | F4104,34104                   | 79              |  |  |  |  |  |

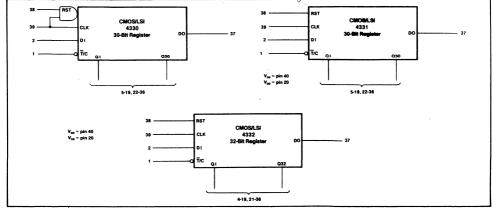

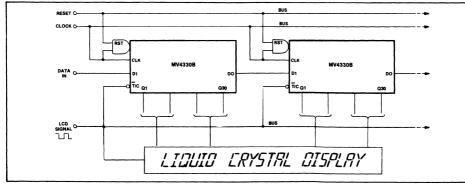

| MV4330/4311                                                                                                      | 30-bit static shift registers                                                         |                               | 101             |  |  |  |  |  |

| MV4332                                                                                                           | 32-bit static shift register                                                          |                               | 101             |  |  |  |  |  |

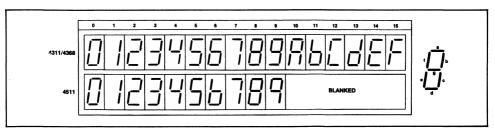

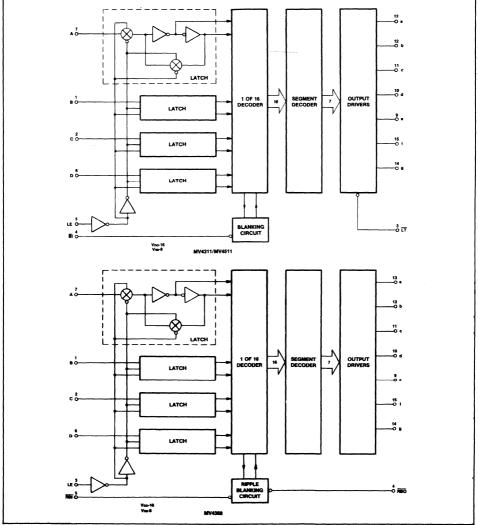

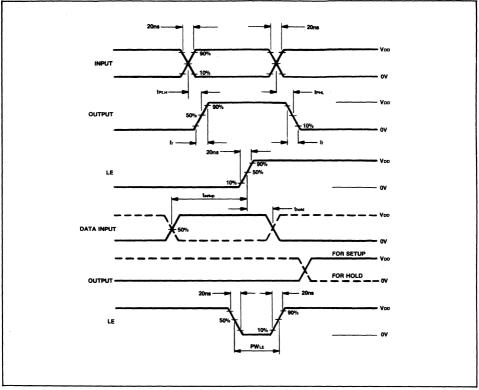

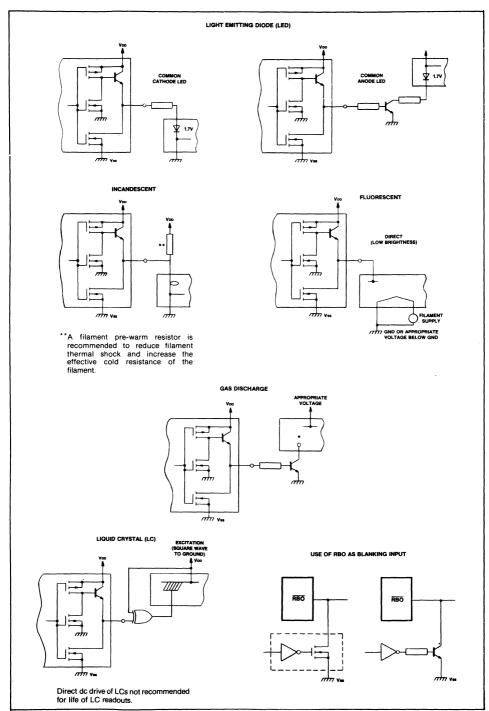

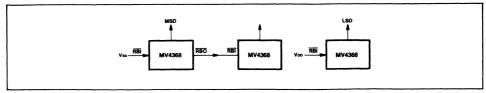

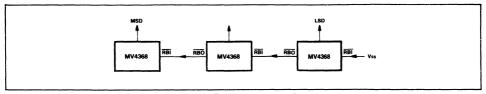

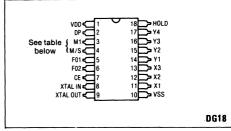

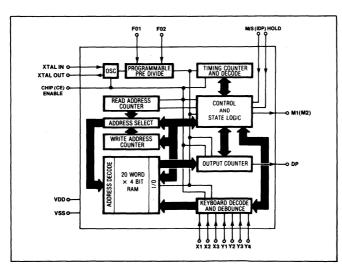

| MV4311<br>MV4368                                                                                                 | Latched Hex to 7-segment display driver                                               | 0000                          | 83              |  |  |  |  |  |

| MV4511                                                                                                           | Latched Hex to 7-segment display driver Latched BCD to 7-segment display              | 9368<br>4511,14511            | 83<br>83        |  |  |  |  |  |

|                                                                                                                  | driver                                                                                | ,                             |                 |  |  |  |  |  |

# Quality data

Plessey Semiconductors have an active **BS9300** and **BS9400** qualification approval programme on a number of products.

Additionally, Plessey Semiconductors are keen to co-operate in pursuing **BS9000** approval on any of the products which it manufactures.

For further information contact the Military Marketing Group at Swindon.

### Plessey Semiconductors QA offers:

a) Factory Approval to

BS9300 for semiconductor devices of Assessed Quality (BSI Certificate 1053/M)

BS9400 for integrated circuits of Assessed Quality (BSI Certificate 1053/M)

CECC 50000 Inspection Organisation to document level 1 (BS9300)

M0020/CECC refers

**DEF STAN 05—21 QC** System requirements for Industry (Equivalent to AQAP—1) Certificate 65752/1/01 refers

b) Additional Release Conditions to

6/49 Defence Quality Assurance Board Certificate (DQAB 38020)

MOD (N) Navy Department Inspection Authority

or Private Sales Plessey's own Certificate of Conformance

Devices are also manufactured, tested and supplied to MIL-STD-833, the US Military Standard; Test Methods and Procedures for Microcircuits, and MIL-M-38510. US Military Specification, Micro-electronics; General Specifications for.

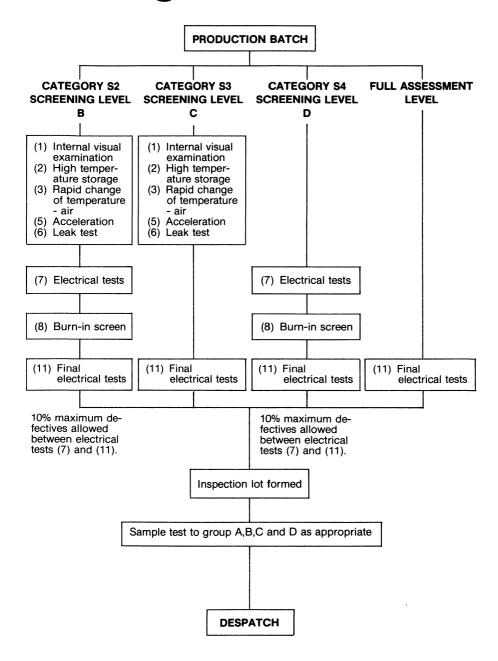

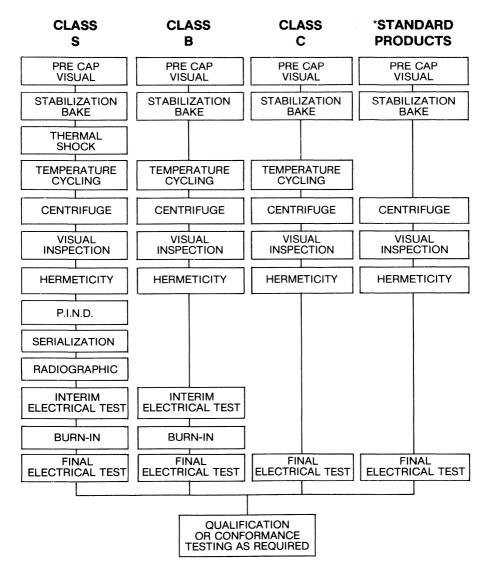

# Screening to BS9400

# Screening to MIL-STD-883

The following Screening Procedures are available from Plessey Semiconductors

<sup>\*</sup>Plessey Semiconductors reserve the right to change the Screening Procedure for Standard Products.

# Semi-custom design

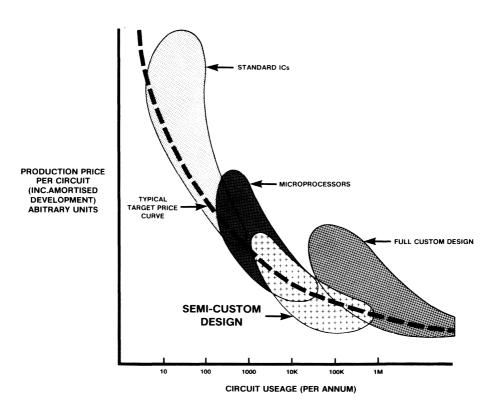

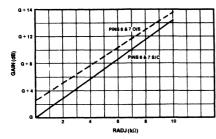

Semi-custom design techniques give users the advantages of integrated circuits dedicated to their applications without incurring the costs associated with full custom design. The techniques are particularly attractive to users with a low-to-moderate annual production potential of 1000 to 100,000 pieces, although these limits are flexible and may depend on the individual circuit. The economics of 'when to choose semi-custom' are illustrated in Fig.1.

Plessey Semiconductors offer semi-custom facilities in N-Channel MOS, CMOS and Bipolar technologies, using the techniques of Microcell, Gate Arrays and Analogue Arrays, the essential characteristics of which are detailed in Table 1.

Fig 1 Areas of application of different categories of integrated circuits

### **MICROCELL**

Microcell is a combination of standard cells with a formalised gate and interconnection procedure. It uses a computer library of gates and other cells which the designer calls up as required, leaving as much or as little space for interconnection as the design necessitates. Each circuit is exactly the right size for its

function, and layout for the interconnection pattern is both straightforward and fast because of the error-correcting digitising technique employed.

The main features of Microcell can be summarised as follows: • From logic diagram to first samples in less than four months • Very high design integrity • A circuit can be produced by any competent logic designer • Minimal extra engineering effort is required • Clock rates of up to at least 2MHz are achievable • Advances in semiconductor technology and circuit design ideas can easily be absorbed into Microcell.

### **GATE ARRAYS**

In the Gate Array, logic elements are pre-positioned and the customer's task is to design the interconnection of those elements (within the space allocated) to achieve the required functions. The cells are not necessarily committed to logic functions, but may in some cases be connected to form simple linear functions. Layout aids and software routines are normally used extensively to assist in the design, verification and testing of these structured devices.

Plessey Semiconductors offer Gate Array techniques in CMOS and ECL. CMOS Gate Arrays offer the following features: • High Speed ISO-CMOS Silicon Gate technology, giving a typical propagation delay of 6ns for a 2-input NAND gate (at 5V and 25°C) • Short turn round time • Inputs and outputs TTL and CMOS compatible and provided with static protection • On-chip power on reset option available • Available to commercial, industrial and military standards.

ECL Gate Arrays - also possessing the advantages of low development charge, increased reliability and fast delivery of samples - would be chosen mainly for the very high speed operating capability.

### ANALOGUE ARRAYS

Plessey Semiconductors' Analogue Array brings Semi-Custom techniques to the designer of linear and other analogue circuits, for applications such as signal processing, amplification, waveform generation and function generation.

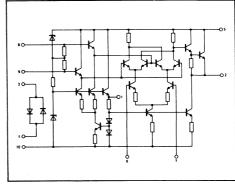

Manufactured on Bipolar Process I the analogue array features: • 159 NPN transistors (4 high current) • 58 PNP transistors • 385 resistors • 20V breakdown voltage • Functional compatibility with Exar and Interdesign • Single layer customisation on a grid system • Device library and simulation facilities.

Comprehensive technical literature on all Plessey Semiconductors' Semi-Custom Facilities is available on request.

| SEMI-CUSTOM OPTION          | TECHNOLOGY             | SPEED       | POWER CONSUMPTION                          | SCALE OF INTEGRATION           | TYP. LEAD TIME<br>TO 1ST SAMPLES |

|-----------------------------|------------------------|-------------|--------------------------------------------|--------------------------------|----------------------------------|

| NMOS<br>Microcell           | NMOS<br>Metal Gate     | 2MHz        | 300mW/1000 gates                           | 500-2500 gates                 | 16 weeks                         |

| Low Power NMOS<br>Microceli | NMOS<br>Metal Gate     | 0.5MHz      | 50mW/1000 gates                            | 500-2000 gates                 | 16 weeks                         |

| CMOS<br>Microceli           | ISO-CMOS               | 10MHz       | 0-150mW/1000 gates*                        | 500-2000 gates                 | 16 weeks                         |

| CMOS<br>Gate Array          | ISO-CMOS               | 8MHz        | 0-150mW/1000 gates*                        | 560,960,1440<br>and 2014 gates | 13 weeks                         |

| ECL<br>Gate Array           | Bipolar<br>Process III | 200MHz      | 75 gates: 900mW max<br>300 gates: 3.5W max | 75 to 600 gates                | 14 weeks                         |

| Bipolar<br>Analogue Array   | Bipolar<br>Process I   | fr = 500MHz | 100mW to 1W**                              | 217 transistors                | 16 weeks                         |

<sup>\*</sup> Depending on speed

<sup>\*\*</sup> Depending on application

# Technical Data

### **ADVANCE INFORMATION**

Advance information is issued to advise Customers of new additions to the Plessey Semiconductors range which, nevertheless, still have 'pre-production' status. Details given may, therefore, change without notice although we would expect this performance data to be representative of 'full production' status product in most cases. Please contact your local Plessey Semiconductors Sales Office for details of current status.

### **MJ1410**

### 8 BIT FORMAT CONVERTER

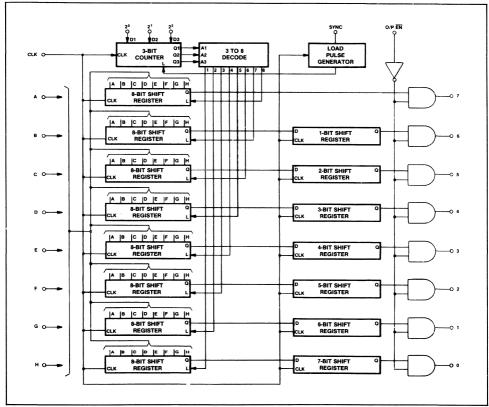

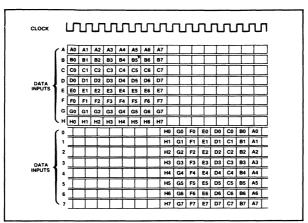

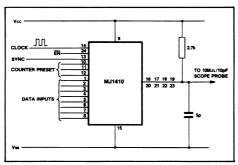

The MJ1410 is realised in N-channel MOS technology and operates from a single 5V supply. The circuit can be clocked from d.c. up to 2.5MHz and has 3-state output buffers capable of driving two LSTTL loads. All inputs are TTL compatible.

The MJ1410 performs the complementary functions of serial-to-parallel and parallel-to-serial data conversion on 8 bits of data. Both these conversions are achieved using the same time-position matrix, which has eight inputs and eight outputs.

An 8-bit parallel word clocked into the eight inputs appears as a serial 8-bit data stream on one of the eight outputs. Successive parallel words at the inputs appear as serial data streams on each of the eight outputs in turn.

Conversely, a serial 8-bit data stream on one of the eight inputs appears as an 8-bit parallel word on the eight outputs. Successive parallel words appearing at the eight outputs correspond to the serial data on each of the eight inputs in rotation.

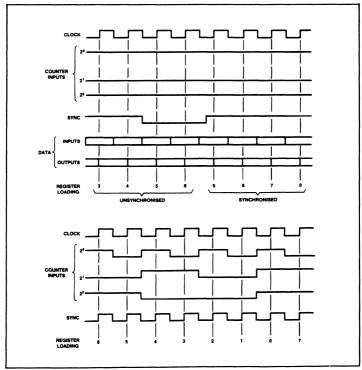

The conversion can be 'programmed' to start in any register by setting the appropriate binary value on the counter pre-load inputs and applying a pulse to the Sync input. If the loading sequence produced by the counter is not required it can be disabled by connecting 'clock' to 'sync'. At each positive clock edge the register loaded will depend on the data on the counter inputs on the previous positive clock edge.

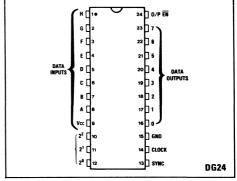

Fig.1 Pin connections

### **FEATURES**

- Single 5V supply.

- Three-state outputs.

- All inputs TTL compatible.

### **FUNCTIONAL DESCRIPTION**

| Pin No.                                   | Title                              | Function                                                                                                                                                                                                        |

|-------------------------------------------|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9 | H G F E D Data inputs C B A Vcc 22 | Data i/p H Data i/p G Data i/p E Data i/p E Data i/p D Data i/p D Data i/p D Data i/p B Data i/p B Data i/p A Positive supply, 5V ± 5% Counter preset i/p bit 2 The counter is preset to the data on these i/ps |

| 11                                        | 21                                 | Counter preset i/p bit 2 \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \                                                                                                                                                    |

| 12                                        | 20                                 | Counter preset i/p bit 0 negative edge on the 'sync' input.                                                                                                                                                     |

| 13                                        | SYNC                               | A negative edge on this i/p initiates the counter preset sequence which causes the conversion cycle to start in the register which corresponds to the binary value of the counter preset i/ps.                  |

| 14                                        | CLOCK                              | System clock                                                                                                                                                                                                    |

| 15                                        | GND                                | Zero volts                                                                                                                                                                                                      |

| 16                                        | 0.7                                | Three state data o/p '0' )                                                                                                                                                                                      |

| 17                                        | 1                                  | Three state data o/p '1'                                                                                                                                                                                        |

| 18                                        | 2<br>3 Data                        | Three state data o/p '2'                                                                                                                                                                                        |

| 19                                        |                                    | Three state data o/p '3' See Figs. 3 and 4                                                                                                                                                                      |

| 20                                        | 4 outputs                          | Three state data o/p '4'                                                                                                                                                                                        |

| 21                                        | 5                                  | Three state data o/p '5'                                                                                                                                                                                        |

| 22                                        | 6                                  | Three state data o/p '6'                                                                                                                                                                                        |

| 23                                        | 7.                                 | Three state data o/p '7'                                                                                                                                                                                        |

| 24                                        | O/P EN                             | A logic '1' on this i/p forces all the data outputs to a high impedance state.                                                                                                                                  |

### **ELECTRICAL CHARACTERISTICS**

Test conditions (unless otherwise stated): Vcc = 5V,  $T_{amb}$  = 22°C  $\pm$  2°C, Test circuit: Fig. 6. Supply voltage Vcc 5V  $\pm$  10%

Ambient operating temperature Tamb -10°C to +70°C

### STATIC CHARACTERISTICS

| Chamastanistia                                     | ١      | Di                                            |      | Value |      |       | Conditions      |  |

|----------------------------------------------------|--------|-----------------------------------------------|------|-------|------|-------|-----------------|--|

| Characteristic                                     | Symbol | Pins                                          | Min. | Тур.  | Max. | Units | Conditions      |  |

| Low level I/P<br>voltage                           | VIL    | 1,2,3,4,<br>5,6,7,8,<br>10,11,12,<br>13,14,24 | -0.3 |       | 0.8  | Volts |                 |  |

| High level I/P<br>voltage                          | Vін    | 1,2,3,4,<br>5,6,7,8,<br>10,11,12,<br>13,14,24 | 2.5  |       | Vcc  | Volts |                 |  |

| Low level I/P<br>current/high level<br>I/P current | lin    | 1,2,3,4,<br>5,6,7,8,<br>10,11,12,<br>13,14,24 |      | 1     | 50   | Ац    |                 |  |

| Low level O/P voltage                              | Vol    | 16,17,18,<br>19,20,21,<br>22,23               |      |       | 0.5  | Volts | ISYNC = 1.6mA   |  |

| High level O/P voltage                             | Vон    | 16,17,18,<br>19,20,21,<br>22,23               | 2.5  |       |      | Volts | ISOURCE = 100uA |  |

| Low level O/P current sync capability              | loL    | 16,17,18,<br>19,20,21,<br>22,23               | -1.6 |       |      | mA    |                 |  |

| High level O/P current source capability           | Іон    | 16,17,18,<br>19,20,21,<br>22,23               | 100  |       |      | Ац    |                 |  |

| OFF state O/P current                              | loff L | 16,17,18,<br>19,20,21,<br>22,23               |      |       | 40   | Αц    | Vout = GND      |  |

|                                                    | loff h | 16,17,18,<br>19,20,21,<br>22,23               |      |       | -40  | μΑ    | Vout = Vcc      |  |

| Power dissipation                                  | Poiss  |                                               | 90   |       | 500  | mW    | Vcc = 5.5V      |  |

### **DYNAMIC CHARACTERISTICS**

|                                                    | Sumbal |      | Value |      | Units | Conditions |

|----------------------------------------------------|--------|------|-------|------|-------|------------|

| Characteristic                                     | Symbol | Min. | Тур.  | Max. | Units | Conditions |

| Max.clock frequency                                | Fmax.  | 2.4  |       | 10   | MHz   |            |

| Min. clock frequency                               | Fmin.  | 0    |       |      | MHz   |            |

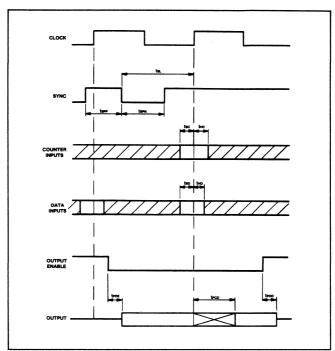

| Sync. pulse width (positive)                       | tspp   | 60   |       |      | ns    | Fig. 6     |

| Sync. pulse width (negative)                       | tspn   | 100  |       |      | ns    | Fig. 6     |

| Lead of sync. clocking edge on positive clock edge | tsı.   | 130  |       | ·    | ns    | Fig. 6     |

| Set up time of counter inputs (20,21,22)           | tsc    | 70   |       |      | ns    | Fig. 6     |

| Hold time of counter inputs                        | tнc    | 60   |       |      | ns    | Fig. 6     |

| Set up time of data inputs (A-H)                   | tso    | 80   |       |      | ns    | Fig. 6     |

### **DYNAMIC CHARACTERISTICS**

| Characteristic                                                     | Cumbai                               | Value |      |       |            |        |

|--------------------------------------------------------------------|--------------------------------------|-------|------|-------|------------|--------|

| Onal acteristic                                                    | Characteristic Symbol Min. Typ. Max. |       | Max. | Units | Conditions |        |

| Hold time of data inputs                                           | tно                                  | 85    |      |       | ns         | Fig. 6 |

| Propagation delay, data<br>out valid from output<br>ENABLE low     | tpde                                 |       |      | 100   | ns         | Fig. 6 |

| Propagation delay, data<br>out disabled from output<br>ENABLE high | tpoo                                 |       |      | 100   | ns         | Fig. 6 |

| Propagation delay, clock to data out valid                         | <b>tp</b> co                         |       |      | 200   | ns         | Fig. 6 |

Fig.2 Block diagram

### **ABSOLUTE MAXIMUM RATINGS**

Voltage on any pin w.r.t. ground = 7V max. Storage temperature = -55°C to +125°C

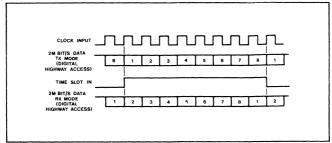

Fig.3 Data conversion

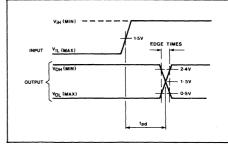

Fig.4 Input and output waveforms

Fig.5 Timing details

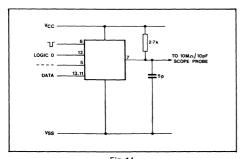

Fig.6 Test conditions

# 2 MBIT PCM SIGNALLING CIRCUIT MJ 1440 HDB3 ENCODER/DECODER

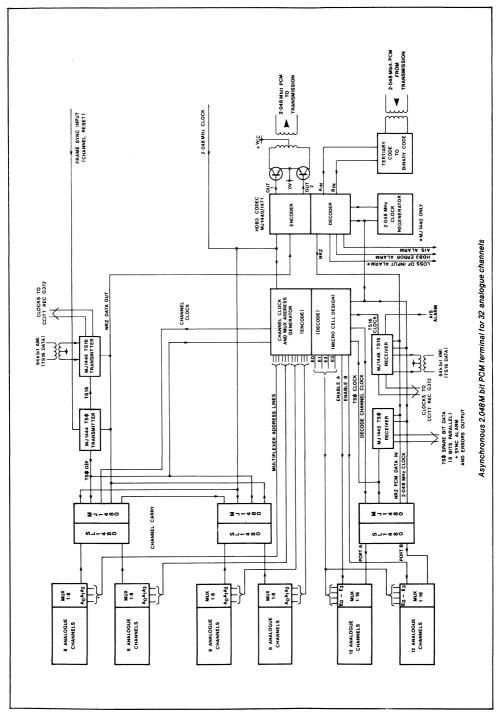

The 2.048 MBit PCM Signalling Circuits comprise a group of circuits which will perform the common signalling and error detection functions for a 2.048 MBit PCM transmission link operating to the appropriate CCITT recommendations. The circuits are fabricated in N-channel metal gate MOS and operate from a single 5 volt supply, relevant inputs and outputs are TTL compatible.

The MJ1440 is an encoder/decoder for the pseudoternary transmission code, HDB3 (CCITT Orange Book Vol III.2 Annex to Rec. G703). The device encodes and decodes simultaneously and asynchronously. Error monitoring functions are provided to detect violations of HDB3 coding, all ones detection and loss of input (all zeroes detection). In addition a loop back function is provided for terminal testing.

###

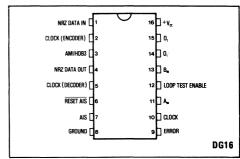

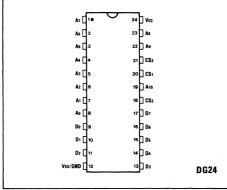

Fig. 1 Pin connections

### **FEATURES**

- $\blacksquare$  5v  $\pm$  5% Supply -50 mA Max

- HDB3 Encoding and Decoding to CCITT rec. G703

- Asynchronous Operation.

- Simultaneous Encoding and Decoding.

- Clock Recovery Signal Generated from Incoming HDB3 Data.

- Loop Back Control.

- HDB3 Error Monitor

- 'All Ones' Error Monitor

- Loss of Input Alarm (All Zeros Detector).

- Decode Data in NRZ Form.

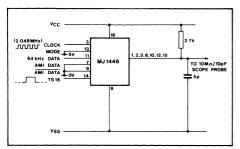

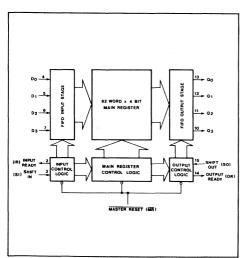

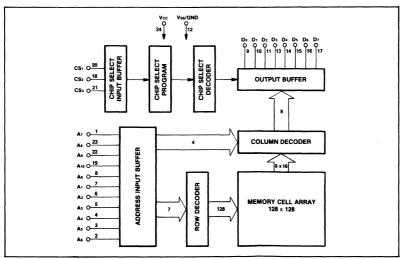

# NRZ DATA IN O CLOCK CLOCK (CHCODER) LOOP TEST ENABLE SWITCH BIN CLOCK (DECODER) AIS CIRCUIT AIS CIRCUIT AIS AIS AIS

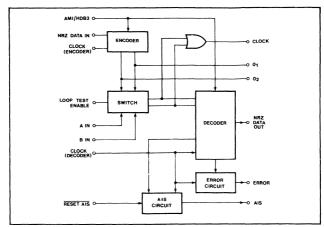

Fig. 2 Block diagram

### **ABSOLUTE MAXIMUM RATINGS**

The absolute maximum ratings are limiting values above which operating life may be shortened or specified parameters may be degraded.

### **Electrical Ratings**

+Vcc 7

### **Thermal Ratings**

Max Junction Temperature 175°C

Thermal Resistance: Chip to Case Chip to Amb.

40°C/Watt 120°C/Watt

### **ELECTRICAL CHARACTERISTICS**

Test conditions (unless otherwise stated): Supply voltage,  $V_{\rm CC} = 5V \pm 0.25V$ Ambient temperature,  $T_{amb} = 0^{\circ}C$  to  $+70^{\circ}C$

### Static characteristics

| Characteristic                                                                                                                           | Symbol                                                                          | Pins                                                                    |                          | Value |                                          | Units                   | Conditions                                                                                                       |

|------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|-------------------------------------------------------------------------|--------------------------|-------|------------------------------------------|-------------------------|------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                          | Oymboi                                                                          | 1 1113                                                                  | Min                      | Тур   | Max                                      | Oilles                  | Conditions                                                                                                       |

| Low level input voltage                                                                                                                  | V <sub>IL</sub>                                                                 | )                                                                       | -0.3                     |       | 0.8                                      | ٧                       |                                                                                                                  |

| Low level input current<br>High level input voltage<br>High level input current<br>Low level output voltage<br>High level output voltage | I <sub>IL</sub> V <sub>IH</sub> I <sub>IH</sub> V <sub>OL</sub> V <sub>OH</sub> | 1,2,5,6<br>10,11,12,13<br>10,14,15<br>3,4,7,9<br>3,4,7,9<br>14,15<br>10 | 2.5<br>2.7<br>2.8<br>2.8 |       | 50<br>V <sub>∞</sub><br>50<br>0.5<br>0.4 | µА<br>V<br>µА<br>V<br>V | V <sub>IL</sub> = 0V  V <sub>IH</sub> = 5V Isink = 80μA Isink = 1.6mA Isource = 60μA Isource = 2mA Isource = 1mA |

| Supply current                                                                                                                           | I <sub>cc</sub>                                                                 |                                                                         |                          | 20    | 50                                       | mA                      | All inputs to 0V<br>All outputs open circuit                                                                     |

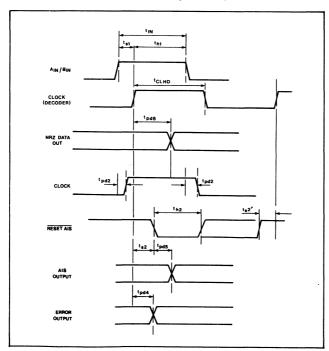

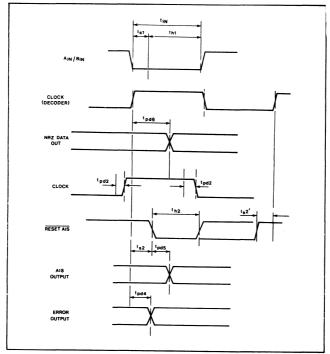

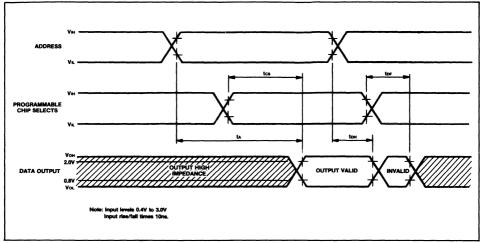

### **Dynamic Characteristics**

| Characteristic                                                       |                     | Value |      |      | Units | Conditions                            |  |

|----------------------------------------------------------------------|---------------------|-------|------|------|-------|---------------------------------------|--|

| Characteristic                                                       | Symbol              | Min.  | Тур. | Max. | Units | Conditions                            |  |

| Max. Clock (Encoder) frequency                                       | fmax <sub>enc</sub> | 4.0   | 10   |      | MHz   | Figs.10, 15                           |  |

| Max. Clock (Decoder) frequency                                       | fmax <sub>dec</sub> | 2.2   | 5    |      | MHz   | Figs.11, 15                           |  |

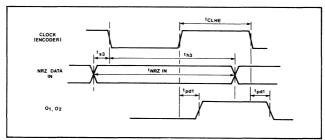

| Propagation delay Clock (Encoder) to O <sub>1</sub> , O <sub>2</sub> | tpd1A/B             |       |      | 100  | ns    | Figs.10, 15. See Note 1               |  |

| Rise and Fall times O <sub>1</sub> , O <sub>2</sub>                  |                     |       |      | 20   | ns    | Figs.10, 15                           |  |

| tpd1A-tpd1B                                                          |                     |       |      | 20   | ns    | Figs.10, 15                           |  |

| Propagation delay Clock (Encoder) to Clock                           | tpd3                |       |      | 150  | ns    | Loop test enable = Figs.13, 15        |  |

| Setup time of NRZ data in to Clock (Encoder)                         | ts3                 | 75    |      |      | ns    | Figs.8, 10, 15                        |  |

| Hold time of NRZ data in                                             | th3                 | 55    |      |      | ns    | Figs.10, 15                           |  |

| Propagation delay A <sub>in</sub> , B <sub>in</sub> to Clock         | tpd2                |       |      | 150  | ns    | Loop test enable = '0' Figs.9, 13, 15 |  |

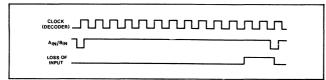

| Propagation delay Clock (Decoder) to loss of input                   |                     |       |      | 150  | ns    |                                       |  |

| Propagation delay Clock (Decoder) to error                           | tpd4                |       |      | 200  | ns    | Figs.12, 15                           |  |

| Propagation delay Reset AIS to AIS                                   | tpd5                |       |      | 200  | ns    | Loop test enable = '0' Figs.14, 15    |  |

| Propagation delay Clock (Decoder) to NRZ data out                    | tpd6                |       |      | 150  | ns    | Figs.9, 11, 15. See Note 2            |  |

| Setup time of A <sub>in</sub> , B <sub>in</sub> to Clock (Decoder)   | ts1                 | 75    |      |      | ns    | Figs.9, 11, 15                        |  |

| Hold time of A <sub>in</sub> , B <sub>in</sub> to Clock (Decoder)    | th1                 | 5     |      |      | ns    | Figs.9, 11, 15                        |  |

| Hold time of Reset AIS = '0'                                         | th2                 | 30    |      |      | ns    | Figs.9, 14, 15                        |  |

| Setup time Clock (Decoder) to Reset AIS                              | ts2                 | 100   |      |      | ns    | Figs.9, 14, 15                        |  |

| Setup time Reset AIS = 1 to Clock (Decoder)                          | ts2′                | 0     |      |      | ns    | Figs.14, 15                           |  |

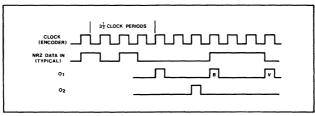

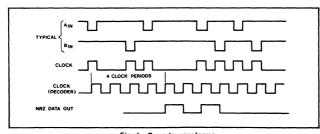

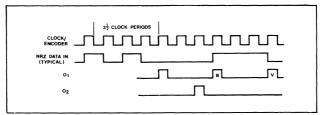

NOTES

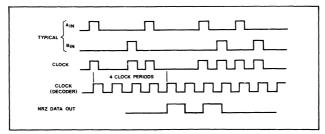

<sup>1.</sup> Encoded HDB3 outputs (O<sub>1</sub>, O<sub>2</sub>) are delayed by  $3\frac{1}{4}$  clock periods from NRZ data in (Fig. 3) 2. The decoded NRZ output is delayed by 4 clock periods from the HDB3 inputs (A<sub>IN</sub>, B<sub>IN</sub>) (Fig. 4)

### **FUNCTIONAL DESCRIPTION**

### Functions Listed by pin number

### 1. NRZ Data in

Input data for encoding into ternary HDB3 form. The NRZ data is clocked-by the negative edge of the Clock (Encoder).

### 2. Clock (Encoder)

Clock for encoding data on pin 1

### 3. Loss of input alarm

This output goes to logic '1' if eleven consecutive zeroes are detected in the incoming HDB3 data. The output is set to logic '0' on receipt of a '1'.

### 4. NRZ data out

Decoded data in NRZ form from ternary HDB3 input data  $(A_{in}, B_{in})$ , data is clocked out by positive going edge of clock (Decoder).

### 5. Clock (Decoder)

Clock for decoding ternary data Ain, Bin,

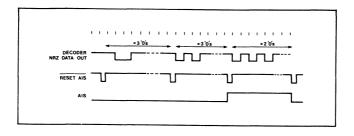

### 6, 7. Reset AIS, AIS

Logic '0' on Reset AIS resets a decoded zero counter and either resets AIS outputs to zero provided 3 or more zeroes have been decoded in the preceding Reset AIS = 1 period or sets AIS to '1' if less than 3 zeroes have been decoded in the preceding Reset AIS = 1 period.

Logic '1' on Reset AIS enables the internal decoded zero counter.

### 8. Ground

Zero volts

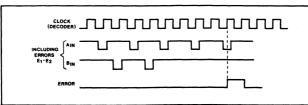

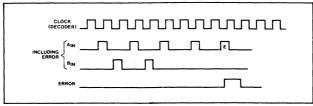

### 9. Error

A logic '1' indicates that a violation of the HDB3 coding has been received i.e. 3 '1's of the same polarity.

### 10. Clock

'OR' function of  $\overline{A}_{in}$ ,  $\overline{B}_{in}$  for clock regeneration when pin 12 = 0', 'OR' function of  $O_1$ ,  $O_2$  when pin 12 = 1'.

### 11,13. A<sub>in</sub>,B<sub>in</sub>

Inputs representing the received ternary HDB3 PCM signal.  $A_{in}=$  '0' represents a positive going '1',  $B_{in}=$  '0' represents a negative going '1',  $A_{in}$  and  $B_{in}$  are sampled by the positive going edge of the Clock (Decoder).  $A_{in}$  and  $B_{in}$  may be interchanged.

### 12. Loop test enable

Input to select normal or loop back operation. Pin 12 = '0' selects normal operation, encode and decode are independent and asynchronous. When pin 12 = '1'  $O_1$  is connected internally to  $A_{\rm in}$ .  $O_2$  is connected internally to  $B_{\rm in}$ . Clock becomes the OR function  $O_1+O_2$ . The delay from NRZ in to NRZ out is 7½ clock periods in the loop back condition.

### 14, 15. O<sub>1</sub>, O<sub>2</sub>

Outputs representing the ternary encoded data for line transmission  $O_1$ = '1' representing a positive going '1',  $O_2$ = '1' represents a negative going '1',  $O_1$  and  $O_2$  may be interchanged.

### 16. V<sub>∞</sub>

Positive supply, 5V ± 5%

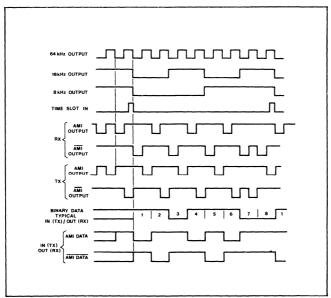

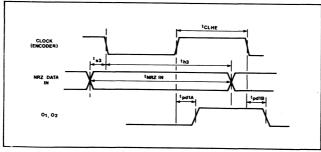

Fig. 3 Encode waveforms

Fig. 4 Decode waveforms

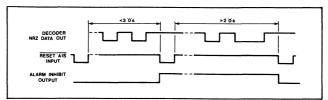

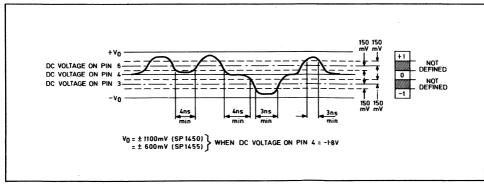

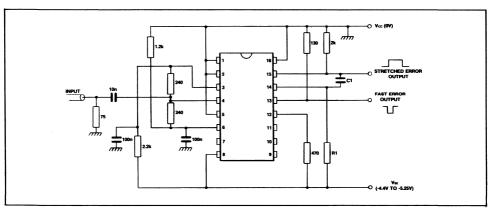

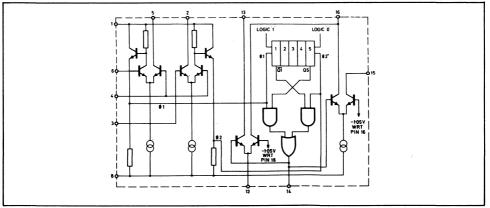

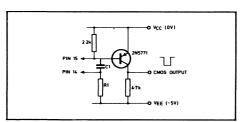

Fig. 5 HDB3 error output waveforms

Fig. 6 AIS error and reset waveforms

Fig. 7 Loss of input waveforms

Fig. 8 Encoder timing relationship

Fig. 9 Decoder timing relationship

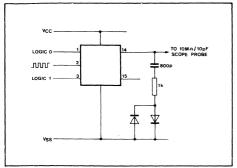

Fig. 10

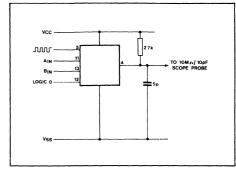

Fig. 11

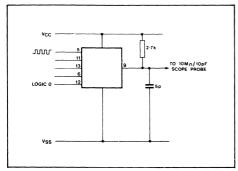

Fig. 12

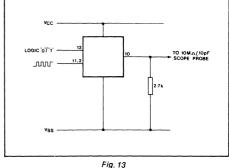

Fig. 14

Fig. 15 Test timing definitions

### **DEFINITION OF THE HDB3 CODE**

Coding of a binary signal into an HDB3 signal is done according to the following rules:

- 1. The HDB3 signal is psuedo-ternary; the three states are denoted B<sub>+</sub>, B\_ and O.

- 2. Spaces in the binary signal are coded as spaces in the HDB3 signal. For strings of four spaces however, special rules apply (see 4. below).

- 3. Marks in the binary signal are coded alternately as B+ and B\_in the HDB3 signal (alternate mark inversion). Violations of the rule of alternate mark inversion are introduced when coding strings of four spaces (see 4, below).

- 4. Strings of four spaces in the binary signal are coded according to the following rules:

- a The first space of a string is coded as a space if the

preceding mark of the HDB3 signal has a polarity opposite to the polarity of the preceding violation and is not a violation by itself; it is coded as a mark, i.e. not a violation (i.e. B<sub>+</sub>, B<sub>-</sub>), if the preceding mark of the HDB3 signal has the same polarity as that of the preceding violation or is by itself a violation.

This rule ensures that successive violations are of alternative polarity so that no DC component is introduced.

- b The second and third spaces of a string are always coded as spaces.

- c The last space of a string of four is always coded as a mark, the polarity of which is such that it violates the rule of alternate mark inversion. Such violations are denoted V<sub>+</sub> or V<sub>-</sub> according to their polarity.

### MJ1440

# 2 MBIT PCM SIGNALLING CIRCUIT MJ 1444

### PCM SYNCHRONISING WORD GENERATOR

The 2.048 Mbit PCM signalling circuits comprise a group of circuits which will perform the common signalling and error detection functions for a 2.048 Mbit 30 channel PCM transmission link operating to the appropriate CCITT recommendations. The circuits are fabricated in N-channel metal gate MOS and operate from a single 5 volt supply. Relevant inputs and outputs are TTL compatible.

The MJ1444 generates the synchronising word in accordance with CCITT recommendations G732. The MJ1445 has been designed to detect this synchronising word when received at the remote end of the transmission system.

The synchronising word is injected onto the PCM data highway during time slot 0 in alternate frames. The spare time slot 0 data bits, bit 1 in every frame and bits 3 to 8 inclusive in alternate frames (i.e. those not containing the synchronising word) are available as parallel inputs and are output onto the PCM data highway.

The data output of the MJ1444 is 'open collector' and can be wire-OR'd directly onto the highway.

The device also provides a time slot 0 channel pulse 'TS0', time slot 0 non-sync. frame 'TS0 SF', and time slot 16 'TS16' outputs.

### **FEATURES**

- 5V ±5% Supply 20 mA Typical

- Fully Conforms to CCITT Recommendation G732

- Outputs Directly Onto PCM Data Highway

- Provides Both Time Slot 0 and Time Slot 16

Channel Pulses

- All Inputs and Outputs are TTL Compatible

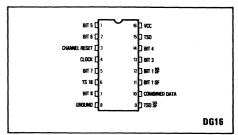

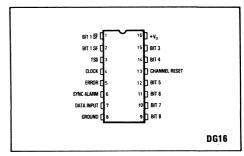

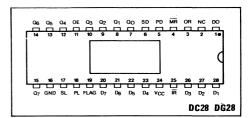

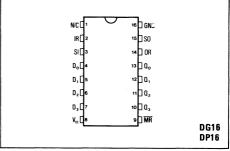

Fig.1 Pin connections

### **ABSOLUTE MAXIMUM RATINGS**

The absolute maximum ratings are limiting values above which operating life may be shortened or specified parameters may be degraded.

### **Electrical Ratings**

+Vcc 7V

Inputs Vcc + 0.5V Gnd - 0.3V

Outputs Vcc. Gnd - 0.3V

### **Thermal Ratings**

Max Junction Temperature 175°C

Thermal Resistance: Chip to Case

35°C/Watt

120°C/Watt

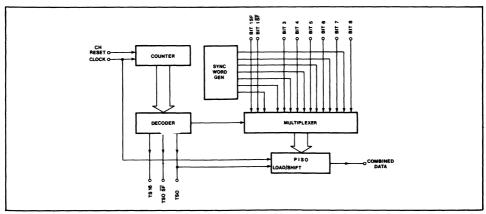

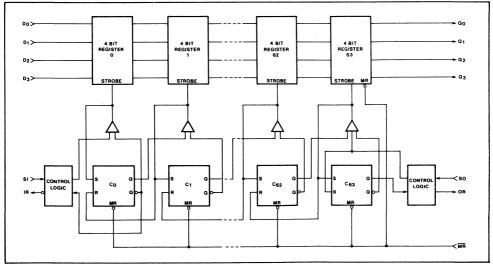

Fig.2 MJ1444 block diagram

### **ELECTRICAL CHARACTERISTICS**

### Test conditions (unless otherwise stated):

Supply voltage, V<sub>CC</sub> = 5V ±0.25V Ambient operating temperature – 10°C to +70°C

### **Static Characteristics**

| Characteristic                                   | Symbol          | Pins                                    | Value |      |                 | Units  | Conditions                                         |  |  |

|--------------------------------------------------|-----------------|-----------------------------------------|-------|------|-----------------|--------|----------------------------------------------------|--|--|

| Cital actoristic                                 | Зушьы           | Fills                                   | Min.  | Тур. | Max.            | Omits  | Conditions                                         |  |  |

| Low level input voltage                          | V <sub>IL</sub> | 1, 2, 3, 4, 5,<br>7, 11, 12, 13,<br>14. | -0.3  |      | 0.8             | ٧      |                                                    |  |  |

| Low level input current High level input current | I <sub>IN</sub> | 11                                      |       | 1    | 50              | μΑ     |                                                    |  |  |

| High level input voltage                         | V <sub>IH</sub> | . 11                                    | 2.4   |      | V <sub>cc</sub> |        |                                                    |  |  |

| Low level output voltage                         | V <sub>OL</sub> | 6, 9, 15<br>10                          |       |      | 0.5<br>0.7      | V<br>V | I <sub>sink</sub> = 2mA<br>I <sub>sink</sub> = 5mA |  |  |

| High level output voltage                        | V <sub>oh</sub> | 6, 9, 15                                | 2.8   |      |                 | ٧      | $I_{\text{source}} = 200 \mu A$                    |  |  |

| High level output leakage current                | I <sub>он</sub> | 10                                      |       |      | 20              | μΑ     | $V_{OUT} = V_{CC}$                                 |  |  |

| Supply current                                   | Icc             |                                         |       | 20   | 40              | mA     | V <sub>CC</sub> = 5.25 V                           |  |  |

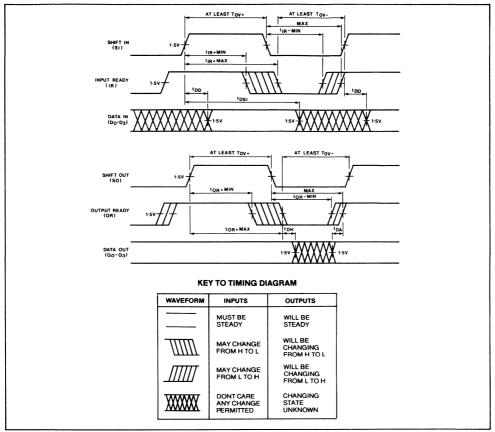

### **Dynamic Characteristics**

| Characteristic                                                           | Symbol           | Va  |           | Value |       | Conditions                     |  |

|--------------------------------------------------------------------------|------------------|-----|-----------|-------|-------|--------------------------------|--|

| Characteristic                                                           | Symbol           |     | Min. Typ. |       | Units | Conditions                     |  |

| Max clock frequency                                                      | F <sub>max</sub> | 3   | 5         |       | MHz   |                                |  |

| Propagation delay, clock to TS0, TS0 SF, TS16 and combined data outputs. | t₽               | 80  |           | 200   | ns    | See Figs.5 and 6               |  |

| Set up time channel reset to clock                                       | T <sub>S1</sub>  | 100 |           | 450   | ns    | f <sub>clock</sub> = 2.048 MHz |  |

| Hold time of channel reset input                                         | t <sub>H1</sub>  | 20  |           | 400   | ns    |                                |  |

| Set up time of bit 1 (SF) to datum B                                     | t <sub>S2</sub>  | 100 |           |       | ns    |                                |  |

| Hold time of bit 1 (SF) wrt datum B                                      | t <sub>H2</sub>  | 300 |           |       | ns    |                                |  |

| Set up time of bit 1 (SF) and data bits 3-8 to datum B                   | t <sub>S2</sub>  | 100 | Ì         |       | ns    |                                |  |

| Hold time of bit 1 ( $\overline{SF}$ ) and data bits 3 — 8 wrt datum B   | t <sub>H2</sub>  | 300 |           |       | ns    |                                |  |

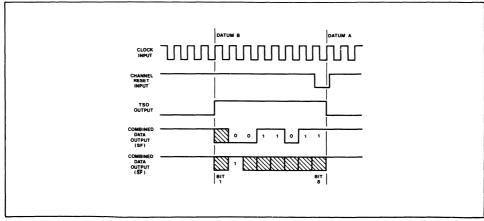

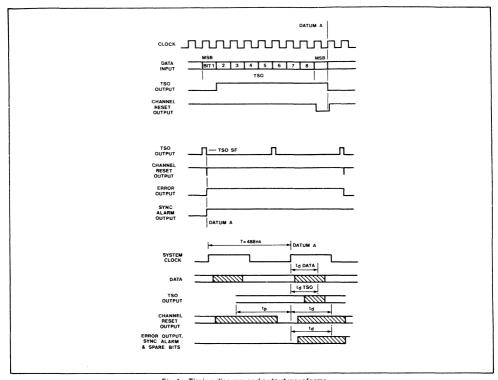

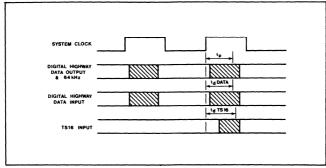

Fig.3 Data timing

### **FUNCTIONAL DESCRIPTION**

### **Functions Listed by pin number**

### 1, 2, 5, 7, 13, 14. Bits 3 to 8

Parallel data on these inputs is asynchronously loaded into bits 3 to 8 of the PISO shift register for transmission during Time slot 0 of non-sync, frames.

### 3. Channel Reset

A low going pulse at this input synchronises the MJ1444 with the other devices at the transmit end of the PCM link. It may be applied as a start pulse or repeated at the same instant in successive frames.

### 4. Clock

System clock input (2.048 MHz for a 2 Mbit PCM system).

### 6 TS1

This output provides a positive pulse equivalent to 8 clock periods during time slot 16 of every 30 + 2 channel PCM frame.

### 8. GND

Zero volts.

### 9. TSO SF

This output provides a positive pulse equivalent to 8 clock periods during time slot 0 of non-sync. frames.

###

Fig.4 Sync. timing

### 10. Combined data

This 'open collector' output injects the contents of the PISO shift register onto the PCM data highway during time slot 0 in successive frames. The contents of the PISO shift register are defined as follows:

|                 | Bit 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 |

|-----------------|-------|---|---|---|---|---|---|---|

| Sync. Frame     | Х     | 0 | 0 | 1 | 1 | 0 | 1 | 1 |

| Non-sync. frame | Х     | 1 | Х | Х | Х | Х | Х | Х |

X—indicates that these bits may be set according to the parallel data inputs.

### 11. Bit 1 SF

Data on this input is asynchronously loaded into bit 1 of the PISO shift register for transmission during time slot 0 of sync. frames.

### 12. Bit 1 SF

Data on this input is asynchronously loaded into bit 1 of the PISO shift register for transmission during time slot 0 of non-sync, frames.

### 15. TS0

This output provides a positive pulse equivalent to 8 clock period during time slot 0 of every 30 channel PCM frame.

### 16. V<sub>CC</sub>

Positive supply, 5V ±5%.

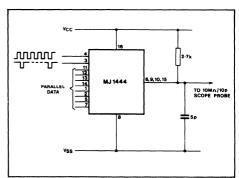

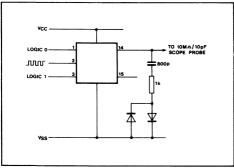

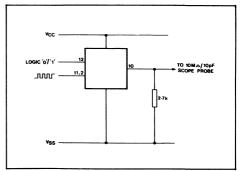

Fig.5 Test conditions (all outputs)

Fig.6 Timing definitions

### MJ1444

# PCM SYNCHRONISING WORD RECEIVER MJ1 445

### 2 MBIT PCM SIGNALLING CIRCUIT

The 2.048 Mbit PCM signalling circuits comprise a group of circuits which will perform the common signalling and error detection functions for a 2.048 MBit 30 channel PCM transmission link operating to the appropriate CCITT recommendations. The circuits are fabricated in N-channel metal gate MOS and operate from a single 5volt supply. Relevant inputs and outputs are TTL compatible.

The MJ1445 establishes synchronisation by detecting the synchronising word when it is received at the remote end of the transmission system. The MJ1444 has been designed to generate this synchronisation word at the sending end of the system in accordance with CCITT recommendation G732.

Corruption of individual synchronisation words is signified by an 'Error' output, loss of synchronisation is indicated by a 'Sync Alarm' output and follows CCITT G732 in that loss of synchronism is assumed when 3 consecutive synchronisation words have been received with errors.

The 'Channel Reset' output goes low for the first period of the clock after time slot 0 in sync frames whenever the MJ1445 has established that the receiver terminal is in synchronisation in order that the rest of the receiver terminal may be reset.

The 'TSO' output is high for a period of 8 bits starting from the end of the first bit of the synchronising word. The spare data bits from the synchronising word are provided as parallel outputs.

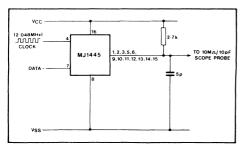

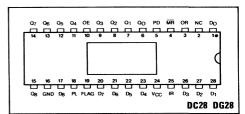

Fig.1 Pin connections

### **FEATURES**

- 5V ±5% Supply ~ 20 mA Typical.

- Conforms to CCITT Recommendation G732

- Synchronising Word Error Monitor

- Out of Sync. Alarm

- All Inputs and Outputs are TTL Compatible

### **ABSOLUTE MAXIMUM RATINGS**

The absolute maximum ratings are limiting values above which operating life may be shortened or specified parameters may be degraded.

### **Electrical Ratings**

+Vcc 7V

Inputs Vcc + 0.5V Gnd - 0.3V

Outputs Vcc, Gnd -0.3V

### Thermal Ratings

Max Junction Temperature 175°C

Thermal Resistance: Chip to Case S5°C/Watt 120°C/Watt

Fig.2 Block diagram MJ1445

### **ELECTRICAL CHARACTERISTICS**

### Test conditions (unless otherwise stated):

Supply voltage,  $V_{CC} = 5V \pm 0.25V$

Ambient temperature, T<sub>amb</sub> = -10°C to +70°C

### Static Characteristics

| Characteristic                                       | Symbol                             | Pins                                         |      | Value |      |       | Conditions                                               |  |

|------------------------------------------------------|------------------------------------|----------------------------------------------|------|-------|------|-------|----------------------------------------------------------|--|

|                                                      |                                    |                                              | Min. | Тур.  | Max. | Units |                                                          |  |

| Low level input voltage                              | V <sub>IL</sub>                    | 4, 7                                         | -0.3 |       | 0.8  | V     |                                                          |  |

| Low level input current } High level input current } | I <sub>IN</sub>                    | 4, 7                                         |      | 1     | 50   | μΑ    |                                                          |  |

| High level input voltage                             | V <sub>IH</sub>                    | 4, 7                                         | 2.4  |       | νœ   | V     |                                                          |  |

| Low level output voltage                             | V <sub>OL</sub>                    | 1, 2, 3, 5, 6<br>9, 10, 11, 12<br>13, 14, 15 |      |       | 0.5  | v     | I <sub>sink</sub> = 2 mA                                 |  |

| High level output voltage<br>Supply current          | V <sub>он</sub><br>I <sub>cc</sub> |                                              | 2.8  | 20    | 40   | mA    | I <sub>source</sub> = 200 μA<br>V <sub>CC</sub> = 5.25 V |  |

### **Dynamic Characteristics**

| Characteristic                                                                            | Symbol              |      | Value |      | Units | Conditions                     |  |

|-------------------------------------------------------------------------------------------|---------------------|------|-------|------|-------|--------------------------------|--|

|                                                                                           | Symbol              | Min. | Тур.  | Max. | Units |                                |  |

| Max. Clock frequency                                                                      | f <sub>max</sub>    | 2.2  | 4.5   |      | MHz   |                                |  |

| Input delay of data input                                                                 | t <sub>d data</sub> | 20   |       | 200  | ns    | f <sub>clock</sub> = 2.048 MHz |  |

| Propagation delay, clock to TS0 output                                                    | t <sub>d TSO</sub>  | 80   |       | 200  | ns    | Fig.3                          |  |

| Propagation delay clock to error output, sync alarm, spare bits and CH. Reset output high | t <sub>a</sub>      | 50   |       | 400  | ns    | Fig.3                          |  |

| Propagation delay, clock to CH. Reset output Low $(T-t_p)$                                | t <sub>p</sub>      | 100  |       | 450  | ns    | Fig.3                          |  |

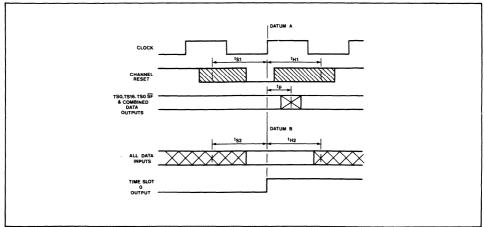

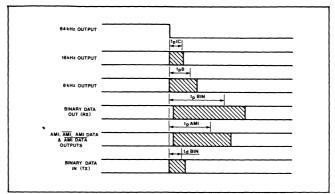

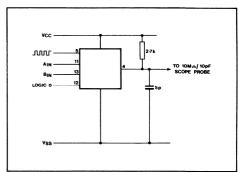

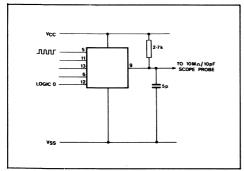

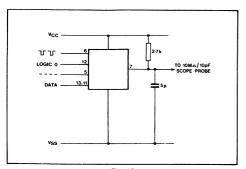

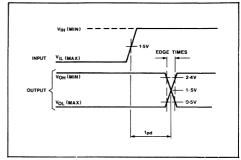

Fig.3 Test conditions, all outputs

### **FUNCTIONAL DESCRIPTION**

### Functions listed by pin number

### 1. Bit 1 SF

This output is set to the level of data bit 1 during time slot 0 of non sync frames. The data becomes true at the end of the first bit of time slot 1.

### 2. Bit 1 SF

This output is set to the level of data bit 1 during time slot 0 of sync frames. The data becomes true at the end of the first bit of time slot 1.

### 3. TS0

This output provides a positive pulse of 8 clock periods in every frame starting from the end of the first bit of the synchronising word of the received data.

### 4. Clock

System clock input (2.048MHz for a 2MBit PCM system).

### 5 Frror

This output goes high at the end of time slot 0 in the 3rd sync frame following the frame with sync word errors. If consecutive sync words occur with errors this output will remain high. If a sync alarm is generated this output will remain high until sync is regained.

This output goes high at the end of time slot 0 output in the 3rd consecutive sync frame containing sync word errors. It returns low at the end of TSO output in the 3rd consecutive frame received correctly (sync and non sync).

### 7. Data input

Serial data (2MBit/s) at this input is clocked through the SIPO shift register and examined by the sync word detector.

### 8. GND

Zero volts

### 9, 10, 11, 12, 14, 15. Bits 3 to 8

These parallel outputs are set to the level of the spare data bits (3 to 8) of time slot 0 of non sync frames. The data becomes true at the end of the first bit of time slot 1.

### 13. Channel reset

This output goes low for the first period of the clock after time slot 0 of the received data as long as synchronisation has been established. This pulse can be used to reset the rest of the receiver terminal.

16.  $V_{CC}$  Positive supply 5 V ±5%.

Fig.4 Timing diagram and output waveforms

### MJ1445

# 2 MBIT PCM SIGNALLING CIRCUIT MJ1 446

## **TIME SLOT 16 RECEIVER AND TRANSMITTER**

The 2.048 Mbit PCM signalling circuits comprise a group of circuits which will perform the common signalling and error detection functions for a 2.048 Mbit 30 channel PCM transmission link operating to the appropriate CCITT recommendations. The circuits are fabricated in N-channel metal gate MOS and operate from a single 5volt supply. Relevant inputs and outputs are TTL compatible.

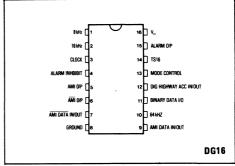

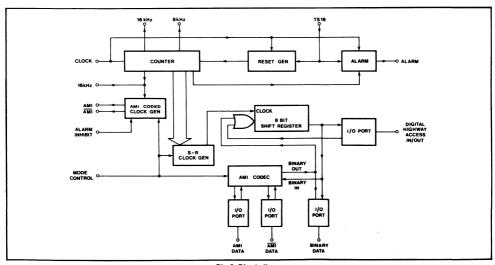

The MJ1446 has two modes of operation dependent on the state of the mode control input. With the mode control high the device is in the transmit mode and with the mode control low the device is in the receive mode.

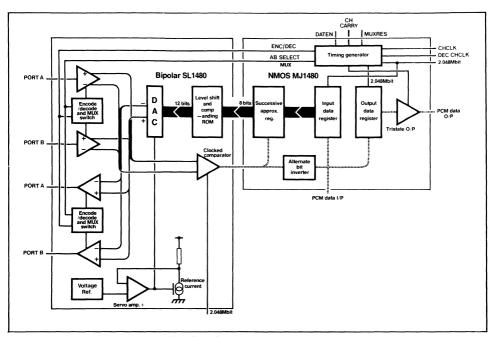

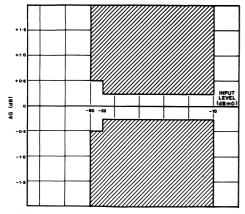

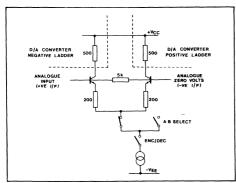

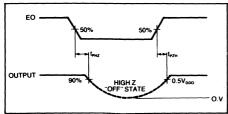

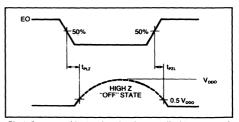

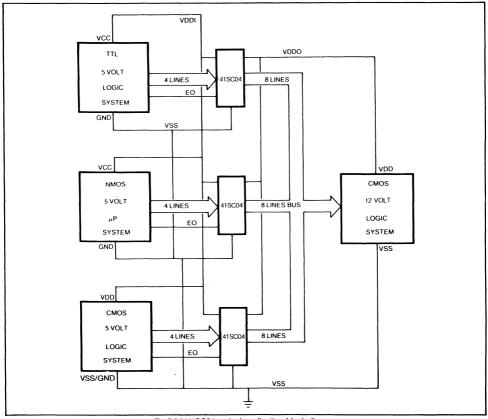

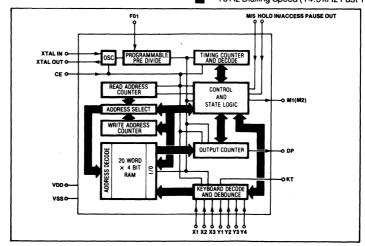

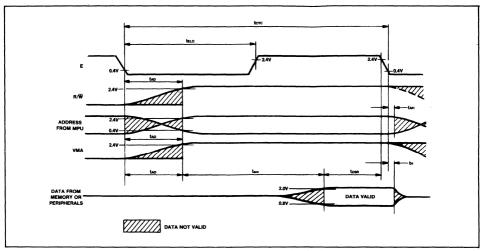

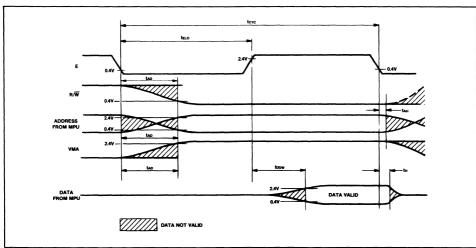

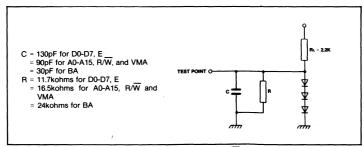

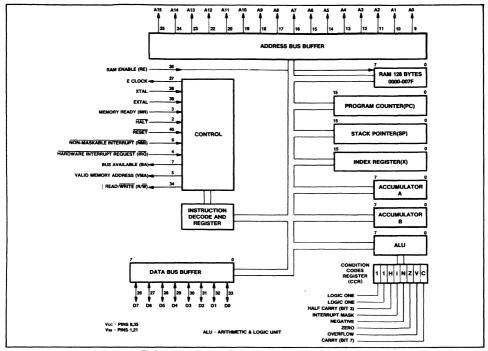

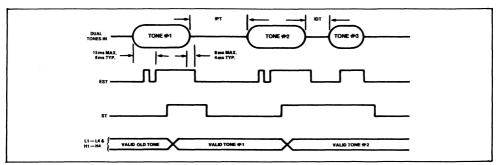

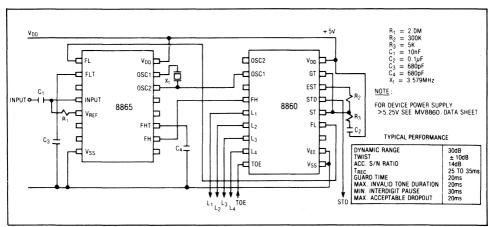

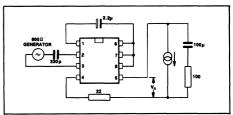

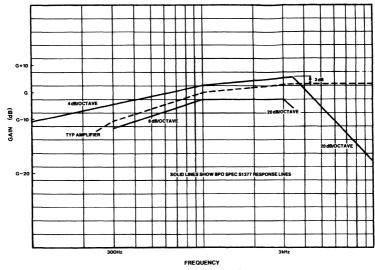

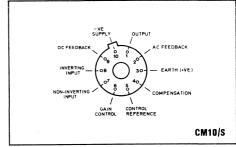

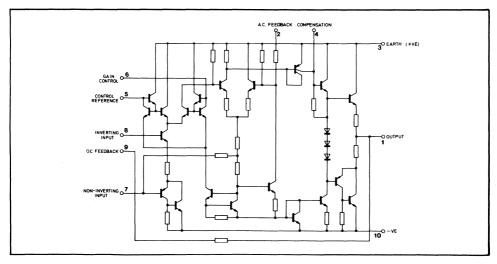

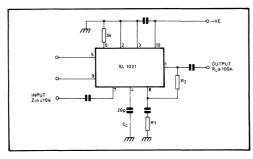

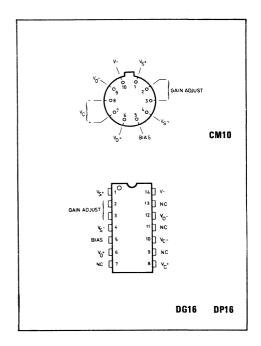

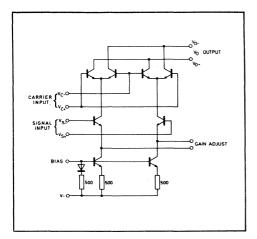

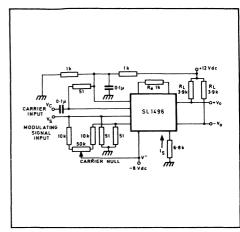

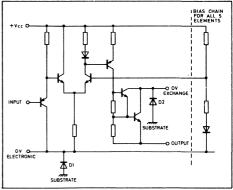

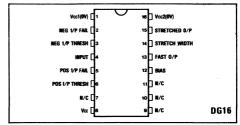

In the transmit mode the device accepts 64kbits/sec signalling information in either binary or AMI format and outputs it at 2Mbits/sec on to the digital highway during time slot 16.